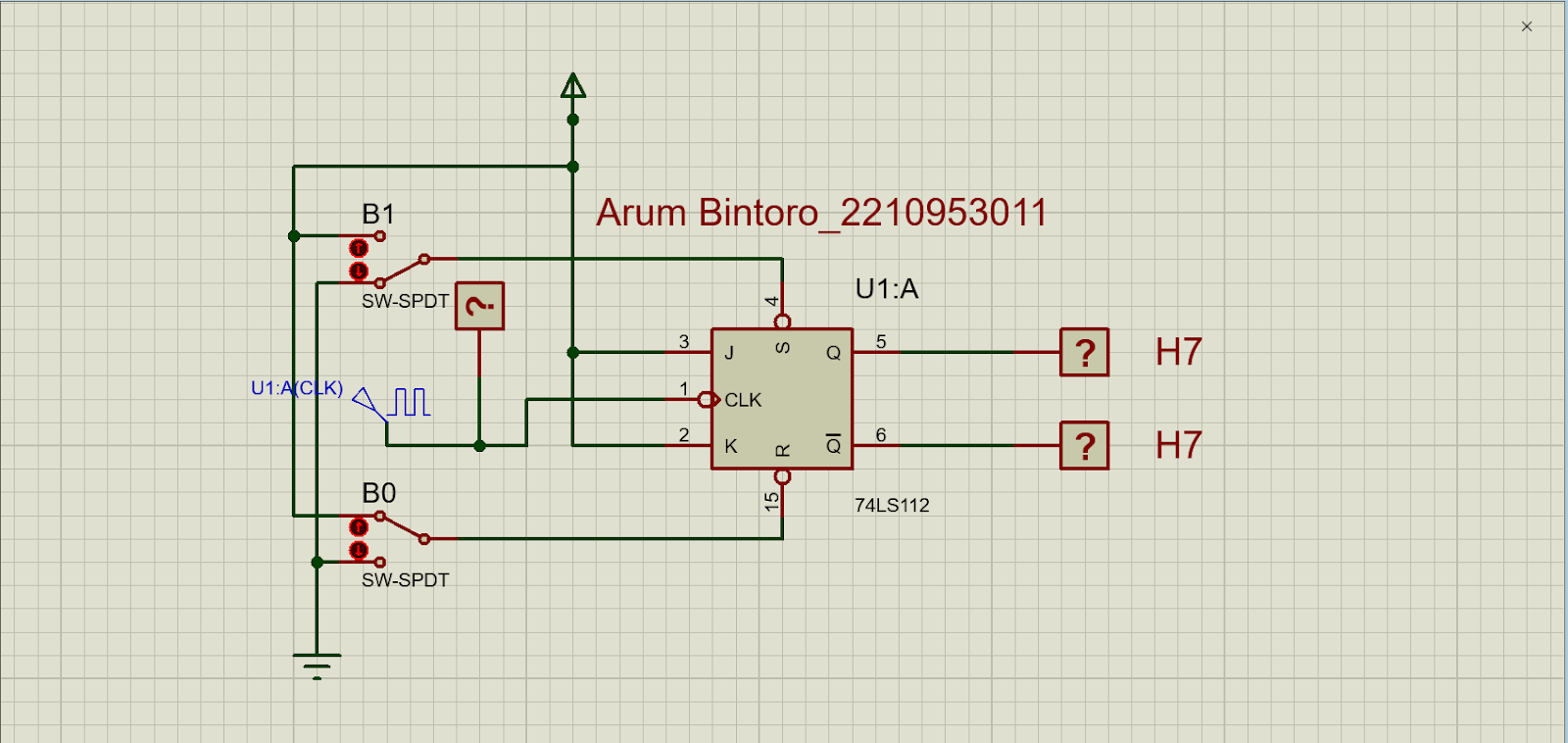

Rangkaian pada gambar adalah rangkaian yang

menggunakan flip-flop JK (IC 74LS112). Berikut adalah penjelasan tentang

komponen utama dan cara kerja rangkaian ini:

Komponen Utama:

- IC

74LS112 (U1):

- Ini

adalah IC yang mengandung dua flip-flop JK.

- Input

utama adalah J, K, dan CLK (clock).

- Output

adalah Q dan Q̅ (komplemen dari Q).

- Switch

SPDT (Single Pole Double Throw):

- B0

dan B1: Switch ini digunakan untuk mengatur logika input J dan K.

- B1:

Switch ini juga digunakan untuk mengatur clock input ke flip-flop.

- VCC

dan Ground:

- VCC

adalah sumber daya positif.

- Ground

adalah referensi tegangan nol.

Cara Kerja Rangkaian:

- Input

dan Output:

- Input

J dan K: Diatur oleh switch B0 dan B1.

- Clock

(CLK): Diatur oleh switch B1.

- Output

Q dan Q̅: Menunjukkan status flip-flop.

- Logika

Flip-flop JK:

- J

= 0, K = 0: Output Q tidak berubah (mempertahankan nilai sebelumnya).

- J

= 0, K = 1: Output Q akan menjadi 0 (reset).

- J

= 1, K = 0: Output Q akan menjadi 1 (set).

- J

= 1, K = 1: Output Q akan toggle (berubah dari 0 ke 1 atau

sebaliknya).

Langkah-langkah Operasi:

- Mengatur

Switch:

- Atur

switch B0 dan B1 untuk memberikan logika input ke J dan K.

- Atur

switch B1 untuk memberikan sinyal clock.

- Memicu

Flip-flop:

- Ketika

clock menerima sinyal pemicu (transisi dari rendah ke tinggi), flip-flop

akan mengevaluasi input J dan K untuk menentukan status output Q dan Q̅.

Contoh:

- Jika

switch B0 diatur ke posisi 1 dan switch B1 diatur ke posisi 0, maka J = 1

dan K = 0, yang berarti output Q akan menjadi 1 (set).

- Jika

switch B0 diatur ke posisi 0 dan switch B1 diatur ke posisi 1, maka J = 0

dan K = 1, yang berarti output Q akan menjadi 0 (reset).

Kesimpulan:

Rangkaian ini menggunakan flip-flop JK untuk menyimpan dan

memanipulasi data logika berdasarkan input J, K, dan sinyal clock. Pengaturan

switch SPDT memungkinkan pengguna untuk mengubah logika input dan memicu

perubahan status flip-flop, yang dapat digunakan dalam berbagai aplikasi

digital seperti counter, register, dan memori.

.jpeg)

.png)