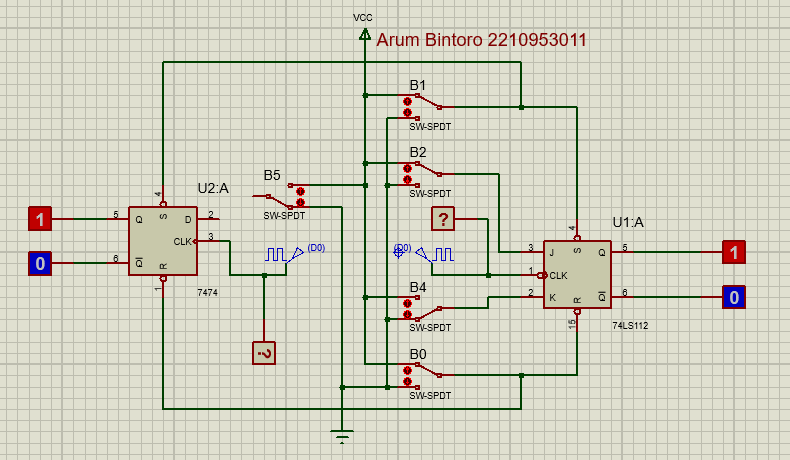

Berdasarkan gambar rangkaian sebelumnya, diketahui prinsip kerjanya adalah sebagai berikut

Rangkaian yang ditampilkan pada gambar adalah sebuah

rangkaian digital yang terdiri dari flip-flop jenis JK dan D. Berikut adalah

penjelasan komponen utama dan fungsi dari rangkaian ini:

- Komponen

IC:

- U1

(74LS112): IC ini adalah flip-flop jenis JK. Flip-flop JK adalah

elemen penyimpanan yang memiliki dua input utama, yaitu J dan K, serta

input clock (CLK). Output dari flip-flop ini adalah Q dan Q̅ (komplemen

dari Q).

- U2

(7474): IC ini adalah flip-flop jenis D. Flip-flop D memiliki input

data (D), input clock (CLK), dan output Q dan Q̅.

- Input

dan Output:

- Input

J dan K pada U1: Input ini dihubungkan ke switch SPDT (Single Pole

Double Throw) yang dikendalikan oleh B0, B1, B2, B4, dan B5.

- Input

D pada U2: Input ini menerima sinyal data (logika 1 atau 0) yang

diatur oleh switch SPDT yang dikendalikan oleh B5.

- Output

Q dan Q̅ dari kedua flip-flop: Output ini digunakan untuk

mengindikasikan keadaan flip-flop.

- Pengendali

Switch (B0, B1, B2, B4, B5):

- Switch

ini digunakan untuk mengatur logika input yang diberikan ke flip-flop.

- Switch

B0, B1, B2, dan B4 digunakan untuk mengatur input J dan K pada flip-flop

JK (U1).

- Switch

B5 digunakan untuk mengatur input D pada flip-flop D (U2).

- Koneksi

Clock:

- Kedua

flip-flop memiliki input clock (CLK) yang digunakan untuk memicu

perubahan status flip-flop berdasarkan input yang diberikan.

- VCC

dan Ground:

- VCC

adalah sumber daya positif untuk rangkaian, sedangkan ground adalah

referensi tegangan nol.

Cara Kerja Rangkaian:

- Flip-flop

JK (U1):

- Ketika

clock menerima sinyal pemicu, status output Q akan berubah berdasarkan

logika input J dan K.

- Jika

J = 0 dan K = 0, output Q tetap sama.

- Jika

J = 0 dan K = 1, output Q akan menjadi 0.

- Jika

J = 1 dan K = 0, output Q akan menjadi 1.

- Jika

J = 1 dan K = 1, output Q akan toggle (berubah dari 0 ke 1 atau

sebaliknya).

- Flip-flop

D (U2):

- Ketika

clock menerima sinyal pemicu, status output Q akan mengikuti logika input

D.

- Jika

D = 0, output Q akan menjadi 0.

- Jika

D = 1, output Q akan menjadi 1.

Kesimpulan:

Rangkaian ini memungkinkan pengguna untuk mengatur dan

memanipulasi status flip-flop dengan menggunakan switch SPDT untuk mengatur

logika input J, K, dan D. Output dari flip-flop dapat digunakan untuk berbagai

aplikasi dalam rangkaian digital, seperti penyimpanan data, pembentukan sinyal,

dan lain-lain.

.png)

Tidak ada komentar:

Posting Komentar